台积电:7nm EUV芯片首次流片成功 5nm明年试产

- 时间:2018-10-10 09:42

- 来源:驱动之家

- 编辑:jhao

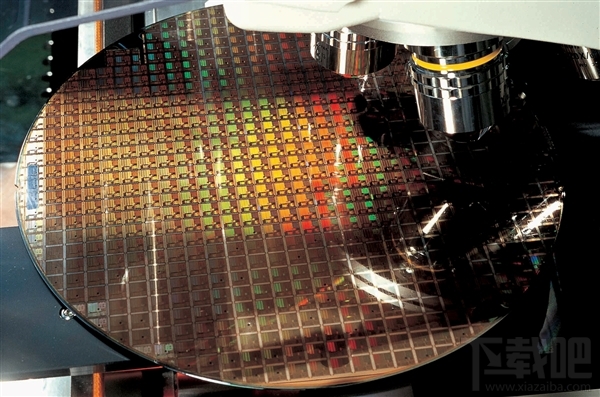

全球一号代工厂台积电宣布了有关极紫外光刻(EUV)技术的两项重磅突破,一是首次使用7nm EUV工艺完成了客户芯片的流片工作,二是5nm工艺将在2019年4月开始试产。

今年4月开始,台积电第一代7nm工艺(CLN7FF/N7)投入量产,苹果A12、华为麒麟980、高通“骁龙855”、AMD下代锐龙/霄龙等处理器都正在或将会使用它制造,但仍在使用传统的深紫外光刻(DUV)技术。

而接下来的第二代7nm工艺(CLNFF+/N7+),台积电将首次应用EUV,不过仅限四个非关键层,以降低风险、加速投产,也借此熟练掌握ASML的新式光刻机Twinscan NXE。

7nm EVU相比于7nm DUV的具体改进公布得还不多,台积电只说能将晶体管密度提升20%,同等频率下功耗可降低6-12%。

如今在7nm EUV工艺上成功完成流片,证明了新工艺新技术的可靠和成熟,为后续量产打下了坚实基础。

台积电没有透露这次流片成功的芯片来自哪家客户,但是想想各家和台积电的合作关系,其实不难猜测。

7nm之后,台积电下一站将是5nm(CLN5FF/N5),将在多达14个层上应用EUV,首次全面普及,号称可比初代7nm工艺晶体管密度提升80%从而将芯片面积缩小45%,还可以同功耗频率提升15%,同频功耗降低20%。

2019年4月,台积电的5nm EUV工艺将开始风险性试产,量产则有望在2020年第二季度开始,正好满足后年底各家旗舰新平台。

台积电5nm工艺的EDA设计工具将在今年11月提供,因此部分客户应该已经开始基于新工艺开发芯片了。

随着半导体工艺的急剧复杂化,不仅开发量产新工艺的成本大幅增加,开发相应芯片也越来越费钱,目前估计平均得花费1.5亿美元,5nm时代可能要2-2.5亿美元。

PS:Intel刚发布的秋季桌面平台仍然都是14nm,而拖延已久的10nm要到明年才能量产,7nm则是遥遥无期,5nm就更别提了。

- 华为MateBook13全面屏轻薄本发售:5199元起

- OPPOR17/R17Pro新年版发布:2799元起

- 联发科Helio P90发布:全新GPU性能提升50%

- 高通骁龙8cx PC平台发布:性能媲美15W酷睿

- 骁龙855信息汇总:高通介绍了这些细节

- 高通骁龙855发布: AI性能提升3倍

- i9-9900K液氮超频6.9GHz:创下跑分世界纪录

- 微软两款折叠屏设备齐曝光:2019年见!

- AMD速龙200GE破解超频3.9GHz:多线程直逼i3-7100

- AMD/Intel处理器缠斗史:为创造伟大产品而生

- Win10新增免密登陆U盘:45美元起

- 1999元!AMD RX 590显卡正式发布:12nm工艺

最近更新

-

无限暖暖兑换码大全 兑换码怎么使用

无限暖暖兑换码大全 兑换码怎么使用

无限暖暖兑换码大全!作为近期爆火的3D虚幻

- 2 DNF手游发生错误游戏结束 11-27

- 3 Farming Simulator25怎么修改播种类型 11-15

- 4 Farming Simulator25怎么设置中文 11-15

- 5 Farming Simulator25怎么种水稻 11-15

- 6 鸣潮v1.4椿成就攻略 11-15

人气排行

-

路由器怎么加速 十个让家里WIFI更快的方法

路由器怎么加速 十个让家里WIFI更快的方法

我们在家的时候会发现家里的wifi虽然被自己建立起来了,但是总觉

-

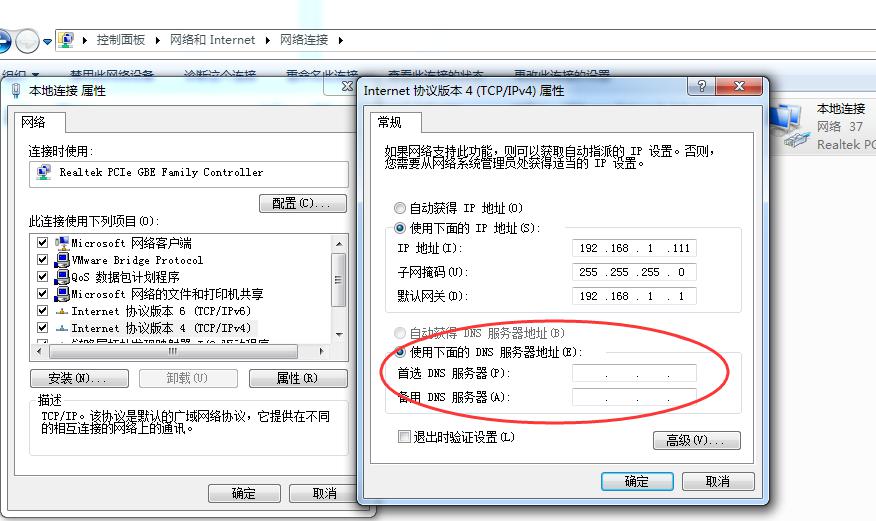

只能上QQ打不开网页怎么办?关于路由器网络设置的那点事

只能上QQ打不开网页怎么办?关于路由器网络设置的那点事

你是否遇到过可以上QQ、旺旺却浏览不了网页?是否遇到过打开一个

-

别被骗,这“U盘”实际是块SSD固态硬盘

别被骗,这“U盘”实际是块SSD固态硬盘

随着科学技术的发展,我们发现进入市场的数码产品越来越小,比如

-

英特尔8代/9代CPU清单曝光:2018年初到来

英特尔8代/9代CPU清单曝光:2018年初到来

今年8月份的时候,英特尔显示带来了面向笔记本平台的8代KabyLake

-

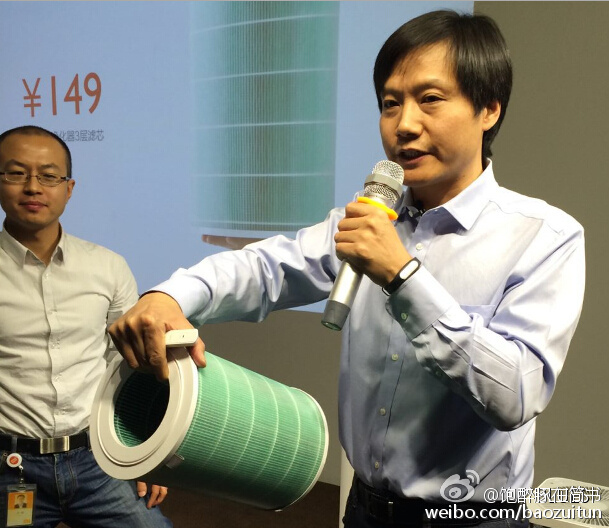

解密小米净化器 为什么我建议你别买

解密小米净化器 为什么我建议你别买

前些日子,打开互联网搜索空气净化器,总能看到这样的新闻:小米

-

2倍TITAN X!AMD发布地球最快显卡Radeon Pro Duo

2倍TITAN X!AMD发布地球最快显卡Radeon Pro Duo

在今天的GDC大会上,AMD正式发布了目前世界最快的显卡——AMDRad

-

联想发布智能路由器newifi:内置私有云插件

联想发布智能路由器newifi:内置私有云插件

联想NBD发布newifi智能路由器,newifi可以通过App、Web与云端进行

-

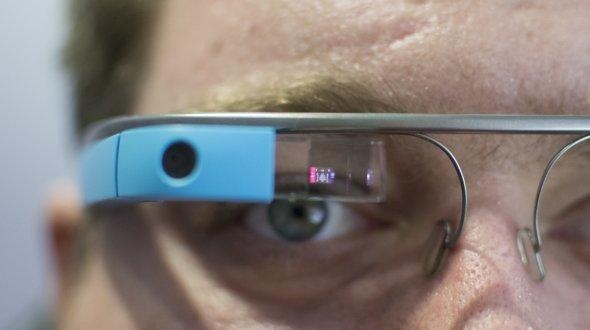

谷歌眼镜可窃取iPad解锁密码 成功率达80%

谷歌眼镜可窃取iPad解锁密码 成功率达80%

曼彻斯特大学的研究员开发了一项可以窃取ipad解锁密码的技术,要

-

小米智能家居产品正式发布!

小米智能家居产品正式发布!

日前,小米通过官方微博宣布将于10月10日上午10点在微博免费首发

-

英特尔计划推动"完全无线缆PC"的发展步伐

英特尔计划推动"完全无线缆PC"的发展步伐

距离让连接个人计算机各种外设间的缆线消失的目标,英特尔只有一