Intel重申:10nm进展良好明年到位

- 时间:2018-10-19 09:13

- 来源:驱动之家

- 编辑:jhao

三星宣布7LPP工艺进入量产,并表示基于EUV光刻技术的7LPP工艺对比现有的10nm FinFET工艺,可以提高20%性能、降低50%功耗、提升40%面积能效。三星电子的代工销售和营销团队执行副总裁Charlie Bae称,随着EUV工艺节点的引入,三星将在半导体行业引领一场变革,“我们相信7LPP不仅是移动和HPC的最佳选择,也适用于更加广泛的尖端应用。”

作为芯片代工行业的后来者,三星是“全球IBM制造技术联盟”中激进派的代表,早早就宣布了7nm时代将采用EUV。今年4月,三星刚刚宣布已经完成了7nm新工艺的研发,并成功试产了7nm EUV晶元,比原进度提早了半年。

相较于传统氟化氩(ArF)浸没技术下的193nm波长深紫外光刻,EUV使用13.5nm波长的极紫外光来曝光硅晶片,且无需使用昂贵的多图案掩模组。与非EUV工艺相比,三星7LPP工艺可将掩模总数减少约20%,为客户节省时间和成本。

根据官方资料,三星EUV的研发始于2000年。作为EUV的先驱,三星还开发了专有功能,例如独特的掩模检测工具,可在EUV掩模中执行早期缺陷检测,从而可以在制造周期的早期消除这些缺陷。

三星7LPP工艺得到了众多Advanced Foundry Ecosystem合作伙伴的支持,其中包括Ansys、Arm、Cadence、Mentor、SEMCO、Synopsys和VeriSilicon等公司。除此之外,三星和上述公司还提供HBM2/2E,GDDR6,DDR5,USB 3.1,PCIe 5.0和112G SerDes等接口IP解决方案。

根据三星的路线,7nm EUV晶元大规模投产时间为2019年秋季,并在位于韩国华城的S3 Fab开始第一批生产。三星没有透露首发使用其7LPP工艺的客户,但暗示第一批芯片将针对移动和HPC应用。

通常而言,三星半导体部门的本家三星电子会第一个采用其尖端制造工艺,因此预计三星2019年的旗舰智能手机将采用7nm SoC。此外,高通也将使用三星的7LPP技术制造其“骁龙5G移动芯片组”。

ASML欣慰之余仍需努力

三星此番宣布7nm EUV工艺进入量产,意味着EUV工艺即将正式商业化,高兴的除了三星自己,当然还有ASML。ASML企业营销副总裁Peter Jenkins在三星公布消息之后表示,“EUV技术的商业化是半导体行业的一场革命,将对我们的日常生活产生巨大影响。我们很高兴与三星及其他领先的芯片制造商就半导体工艺制造的这一根本性转变进行合作。”据了解,ASML在本季度出货了5台EUV光刻机,上季度出货7台,预计下季度还将出货6台EUV光刻机,2018全年出货量将达到18台,2019年的出货量还将增至30台,看起来确实是在稳步攀升。

不过EUV工艺的量产只是一个开始,三星生产7LPP晶元所使用的ASML EUV光刻机,使用40对蔡司镜面构成光路,每个镜面的反光率为70%。这也就是说,EUV光束通过该系统中的每一对镜面时都会减半,在经过40对镜面反射后,只有不到2%的光线能投射到晶元上。

到达晶圆的光线越少,光刻所需的曝光时间就越长,相应的生产成本也就越高。为了抵消镜面反射过程中的光能损耗,EUV光源发出的光束必须足够强,这样才能与现在非常成熟的DUV光刻技术比拼时间成本。

多年以来,光照亮度的提升始终未能达到人们的预期,ASML的EUV产品市场负责人Hans Meiling曾表示,人们严重低估了EUV的难度。现在的NXE:3400B型EUV光刻机每小时只能处理125片晶元,效率仅有现今DUV的一半。ASML公司计划在明年下半年推出NXE:3400C光刻机,晶元处理能力可提升至155片,这对改善EUV工艺的产能很有帮助。

Intel重申10nm工艺进展良好

Intel作为全球最大的半导体企业,在半导体工艺方面一直保持着领先地位,并且引领了大量全新技术的发展。不过近几年,Intel半导体工艺的发展速度似乎逐渐慢了下来,比如14nm工艺竟然用了三代,10nm工艺也被竞争对手抢先。

不知是出于巧合还是商业敏感,就在三星宣布7LPP工艺进入量产的前三天,Intel集团副总裁Venkata Murthy Renduchintala在周一的一封公开信中,重申了Intel的10nm工艺目前进展良好,良率正在逐步提升,与此前4月份Intel官方分享的时间表一致,10nm处理器预计在2019年底的假期季节上市。

从技术角度来看,由于晶体管制造的复杂性,每代晶体管工艺中有面向不同用途的制造技术版本,不同厂商的代次之间统计算法也完全不同,单纯用代次来对比是不准确的。目前业内常用晶体管密度来衡量制程水平,Intel最新10nm制程的晶体管密度甚至反而要比三星、台积电的7nm制程更高。

国外网站Semiwiki曾讨论过三星的10nm、8nm以及7nm制程的情况,其中10nm制程的晶体管密度是55.5MTr/mm,8mm是64.4MTr/mm,7nm也不过101.23MTr/mm,堪堪超过Intel 10nm制程的100.8MTr/mm一点点。如果Intel的10nm处理器能在2019年底如期上市,倒也算得上“好饭不怕晚”。

不过值得注意的是,Venkata Murthy Renduchintala在信中提到,Intel领导晶圆制造业务的高管Sohail Ahmed将在下个月退休,他的职位未来将由三位高管承担,Intel计划将晶圆制造业务拆分为技术开发、制造/运营及供应链三个部分,这三位高管负责向Venkata Murthy Renduchintala汇报工作。

具体来说,Intel晶圆制造业务的技术开发由Mike Mayberry接任,他现在是Intel的CTO及实验室负责人,不过后一个职位之后将由Rich Uhlig临时接管,负责实验室工作;Intel的晶圆制造及运营业务将由Ann Kelleher领导,他曾经与Sohail U. Ahmed一起负责运营技术及制造业务部门;Intel的供应链将由Randhir Thakur负责管理。

此举被外界视为Intel拆分晶圆制造业务的开始,不过据了解到的情况,实际上在更早之前,就有传闻称Intel准备在2020到2021年间开始剥离半导体工厂业务。Intel方面对技术及制造业务部门的改组没有发表任何评论。

- 华为MateBook13全面屏轻薄本发售:5199元起

- OPPOR17/R17Pro新年版发布:2799元起

- 联发科Helio P90发布:全新GPU性能提升50%

- 高通骁龙8cx PC平台发布:性能媲美15W酷睿

- 骁龙855信息汇总:高通介绍了这些细节

- 高通骁龙855发布: AI性能提升3倍

- i9-9900K液氮超频6.9GHz:创下跑分世界纪录

- 微软两款折叠屏设备齐曝光:2019年见!

- AMD速龙200GE破解超频3.9GHz:多线程直逼i3-7100

- AMD/Intel处理器缠斗史:为创造伟大产品而生

- Win10新增免密登陆U盘:45美元起

- 1999元!AMD RX 590显卡正式发布:12nm工艺

最近更新

-

无限暖暖兑换码大全 兑换码怎么使用

无限暖暖兑换码大全 兑换码怎么使用

无限暖暖兑换码大全!作为近期爆火的3D虚幻

- 2 DNF手游发生错误游戏结束 11-27

- 3 Farming Simulator25怎么修改播种类型 11-15

- 4 Farming Simulator25怎么设置中文 11-15

- 5 Farming Simulator25怎么种水稻 11-15

- 6 鸣潮v1.4椿成就攻略 11-15

人气排行

-

路由器怎么加速 十个让家里WIFI更快的方法

路由器怎么加速 十个让家里WIFI更快的方法

我们在家的时候会发现家里的wifi虽然被自己建立起来了,但是总觉

-

只能上QQ打不开网页怎么办?关于路由器网络设置的那点事

只能上QQ打不开网页怎么办?关于路由器网络设置的那点事

你是否遇到过可以上QQ、旺旺却浏览不了网页?是否遇到过打开一个

-

别被骗,这“U盘”实际是块SSD固态硬盘

别被骗,这“U盘”实际是块SSD固态硬盘

随着科学技术的发展,我们发现进入市场的数码产品越来越小,比如

-

英特尔8代/9代CPU清单曝光:2018年初到来

英特尔8代/9代CPU清单曝光:2018年初到来

今年8月份的时候,英特尔显示带来了面向笔记本平台的8代KabyLake

-

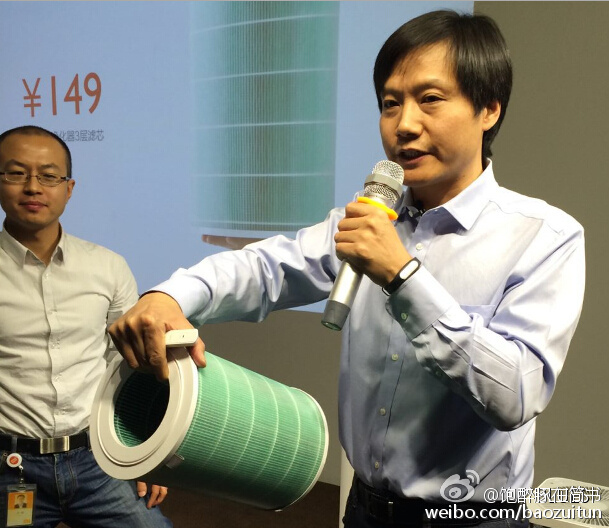

解密小米净化器 为什么我建议你别买

解密小米净化器 为什么我建议你别买

前些日子,打开互联网搜索空气净化器,总能看到这样的新闻:小米

-

2倍TITAN X!AMD发布地球最快显卡Radeon Pro Duo

2倍TITAN X!AMD发布地球最快显卡Radeon Pro Duo

在今天的GDC大会上,AMD正式发布了目前世界最快的显卡——AMDRad

-

联想发布智能路由器newifi:内置私有云插件

联想发布智能路由器newifi:内置私有云插件

联想NBD发布newifi智能路由器,newifi可以通过App、Web与云端进行

-

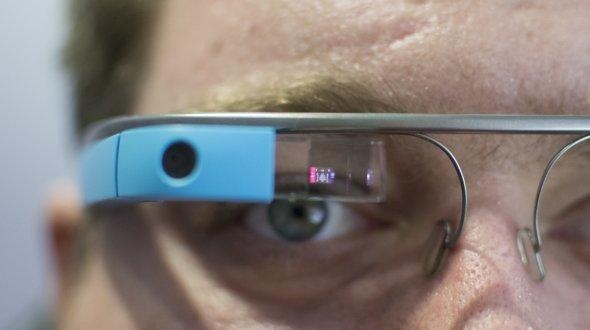

谷歌眼镜可窃取iPad解锁密码 成功率达80%

谷歌眼镜可窃取iPad解锁密码 成功率达80%

曼彻斯特大学的研究员开发了一项可以窃取ipad解锁密码的技术,要

-

小米智能家居产品正式发布!

小米智能家居产品正式发布!

日前,小米通过官方微博宣布将于10月10日上午10点在微博免费首发

-

英特尔计划推动"完全无线缆PC"的发展步伐

英特尔计划推动"完全无线缆PC"的发展步伐

距离让连接个人计算机各种外设间的缆线消失的目标,英特尔只有一